ARM升级服务器芯片架构向x86宣战

ARM最近要求芯片制造商在制造Cortex单片架构服务器芯片时,增加更多内核和缓存。ARM希望通过升级ARMv7和未来的ARMv8中的片上(SoC)缓存和主内存控制器来与英特尔的x86架构在服务器市场的统治地位发起挑战。

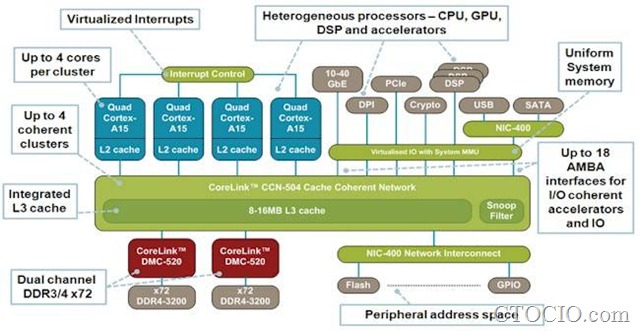

ARM昨日在Linely Tech处理器大会上展示了最新的CoreLink CCN-504缓存一致性技术,可以将4颗四核Cortex-A15处理器(8-16MB缓存)整合成一个处理网络。该处理网络是片上系统的中心,连接各个内核、缓存、主内存控制器以及位于处理器之外的外设控制器。

很多芯片制造商将采用升级后的CoreLink缓存网络,用来连接内核上的控制器,甚至会有厂商用缓存一致性网络来将ARM处理器核心和GPU或其他协处理器连接成一个整体,在单一内核上实现混合处理。

这种CPU和GPU混合的异构计算将共享L3缓存,大幅减少了CPU和GPU之间数据交换,在未来的超级计算应用中将节省大量时间和能源。通过L3缓存整合CPU和GPU的方法被ARM称为big.LITTLE,当然,对于业界来说,这还只是一个非正式的代号。

ARM预计企业将对在SoC上整合DSP数字信号处理器和其他加速器有兴趣,其中一个有趣的实现是Adapteva开发的Epiphany RISC协处理器。想象一下吧,把两个四核ARM芯片和两个64核Epiphany协处理器整合到一个SoC上。

ARM的新CoreLink CCN-504缓存一致性网络架构

升级后的ARM缓存一致性网络把目前Cortex-A9架构技术支持的内核数量提高了一倍,同时兼容Cortex-A15设计以及其派生设计和明年即将发布的ARMv8设计。

Applied Micro Circuits非常有可能成为第一个生产ARMv8架构服务器芯片(X-Gene处理器)的厂商,但目前还不清楚Applied Micro是否采用CoreLink整合内核与缓存。目前,存储芯片和阵列厂商LSI和ARM服务器芯片创业公司Calxeda(刚刚完成5500万美元第二轮融资)是首批获得新缓存电路授权的厂商。

新的ARM缓存控制器网络的带宽约1TB/秒,运行的时钟频率与CPU相同。总线带宽为128位,采用Snoop目录技术最小化广播数据量,这也是实现L3缓存一致性的必要技术。

此外,ARM还提供了一个新的内存控制器——CoreLink DMC-520,将与CCN-504协同工作。此类控制器支持DDR3、低电压DDR3和DDR4内存条。DDR4内存规范刚刚由JEDEC固态技术协会发布,额定电压为1.2伏,而不是DDR3的1.5或1.35伏,DDR4的内存容量为2-16Gb,预计2014年DDR4将逐步进入市场,2015年成为主流产品。

ARM表示CCN-504缓存一致性网络未来设计家族的一员,所以不用为ARM服务器芯片的可扩展性担忧。据悉,昨日ARM的顶级授权合作商已经拿到了CCN-504和DMC-502的设计。

Via Theregister

第一时间获取面向IT决策者的独家深度资讯,敬请关注IT经理网微信号:ctociocom

除非注明,本站文章均为原创或编译,未经许可严禁转载。

相关文章: